GDP-XL

Design & IP Management

Global Design Platform maximizes collaboration efficiency

IC Manage GDP-XL (Global Design Platform) is the industry’s highest performance, most reliable & scalable global design data & IP management system. GDP-XL enables companies to efficiently collaborate on single and multi-site designs.

GDP-XL streamlines the process of building complex IP and releasing SoCs to fabrication. Designers can dynamically track, control, and distribute library, IP, and SOC design data, including configurations and properties — enhancing product quality, engineering productivity, and bug dependency tracking.

GDP-XL is adaptable to both analog and digital workflows and includes integrations with leading custom design tools such as those from Cadence and Synopsys.

Multisite design & IP management

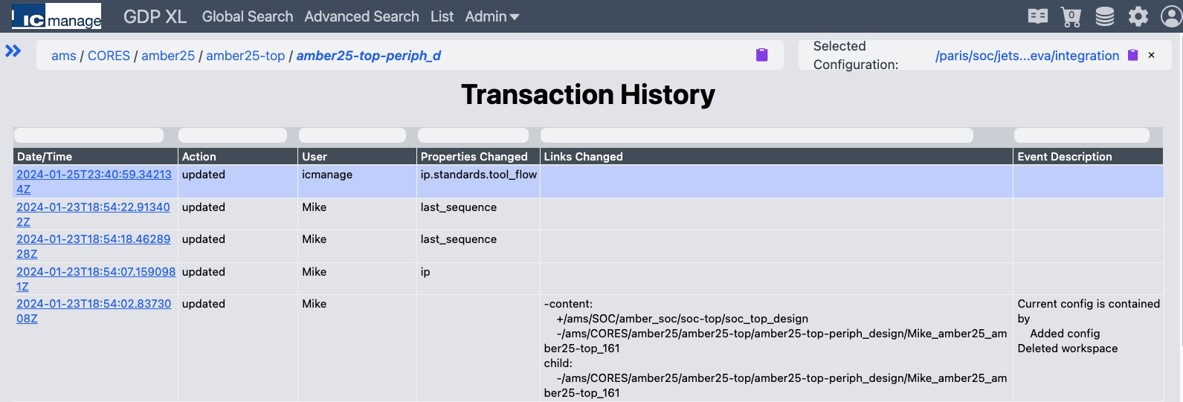

GDP-XL scales from small teams to 1000s of users collaborating 24×7 across global design centers. Every design change is captured with an atomic change list, and each component has its own change-by-change audit. It has fully automated release and derivative creation and tracking, with tracing extending to additional services: bug tracking, requirements management, and product lifecycle management.

GDP-XL’s modern C++ database architecture delivers a 10-100X speedup over design and IP management systems whose database architectures are based on interpreted languages such as Java.

Below is GDP-XL’s representative performance on a 1 million element stress test vs a typical competitive design & IP management system.

- GDP-XL 19 seconds

- Competitors 20-30 minutes

In the above stress test, the GDP-XL server checked all security rules for each record including groups, roles, object permissions, inherited permissions, property-level permissions, then computed and passed 1M+ graph records to the client.

GDP-XL has tight bug tracking linkage, enabling all bugs and bug fixes associated with each design element or IP block to be recorded automatically.

This allows engineers & team leaders to identify bugs, trace their dependencies and propagate fixes across all versions of the design elements or IP over time.

Unmatched Time Machine functionality

The Time Machine feature provides full revision control of all database states, enabling versioning of every change made after the creation of a project, workspace, and configuration.

By using the Time Machine’s intuitive interface, users can access all versions, providing complete audit control and the ability to recover any state at any time. Design engineers, IT, information security, and management are empowered to fully trace, compare, all modifications to any database object or property, and recover prior versions. As a result, the system supports recovery from errors, evolving requirements, malicious actions, or system-induced corruptions.

Designed to operate natively on the server, the GDP-XL Time Machine safeguards information from unauthorized access, ensuring security across all object states without compromising the performance of the design & IP management system.

The unmatched custom business logic automation in IC Manage GDP-XL enables design teams to independently program custom features and logic using transparent and modifiable pre-compiled Python libraries as plugins. This approach enables development teams to swiftly implement new features without any downtime or the need for design management version upgrades.

Because the logic and features are implemented as plugins, design teams can integrate automation and scripting seamlessly, without altering the client or server, unlike traditional design management systems, including IC Manage GDP Classic. This flexibility ensures that enhancements can be made quickly and efficiently.

The business logic scripts leverage IC Manage’s extensive design management expertise accumulated based on input from hundreds of customers.

GDP-XL offers bank-grade security to protect your data at all times and enables comprehensive security auditing.

First, GDP-XL uses HTTPS for its graphical user interface, command-level interface, and web API; its database API is never exposed to users. Additionally, its server-side, role-based permissions leverage a fast, powerful C++ engine, and support role inheritance, project directory inheritance, and property protection.

Further, GDP-XL includes continuous data protection. At runtime, it employs SSL transport encryption and strong authentication to encrypt and decrypt all data sent and received using AES-256-CTR. It automatically uses hardware acceleration to enhance encryption and decryption speed when available.

GDP-XL’s software-only implementation offers improved performance and increased resistance to side-channel attacks. It requires Advanced Encryption Standard New Instructions (AES-NI), which has been supported by most Intel and AMD microprocessors from the last decade.

These bank-grade security features in GDP-XL are absent in other design management systems, which typically utilize lower-level security that exposes data to users, creating potential attack vectors. Client-side permission checks introduce risks of snooping and control by malicious actors or system errors. Additionally, no data-level security, data encryption, or security auditing is available in these other systems.

Integrated IP management

GDP-XL includes IC Manage IP Central semiconductor IP management, which pulls together all company internal and third-party IP from any design data management system, delivering a searchable IP catalog that every designer can access.

Engineers use IP Central’s Google-like user interface and IP catalog filters to search for the best IP for their design, and then can automatically render an HTML datasheet.

IP Central scales to 100M+ IP objects, binding IP from any combination of commercial or open-source design management systems, without overhead of moving the IP to a new repository. IP Central is tightly integrated with bug tracking, so design and verification teams to view and trace the bug history for every IP across all versions and designs.

Reduces FPGA Design Management Complexity

GDP-XL is highly effective for FPGA design and IP management. It is fully integrated with major FPGA development tools, including AMD Vivado and Altera Quartus.

GDP-XL’s partition and assembly approach eliminates the complexity of managing mega Git repositories or manually keeping track of 10 to 100,000 small repositories. IC Manage GDP-XL has been used to design every FPGA product at AMD and Altera for more than a decade.

What users are saying

Viasat | Keith Steele

“We’ve taped out many RFICs that are now in orbit, ground stations, airliners and homes. IC Manage [GDP-XL] allows us to maintain the level of rigorous database control and tracking on these critical RFIC designs. IC Manage is the behind the scenes tool that is a big part of our RFIC design success.”

Rivos| Brian Campbell

“As our custom IP team at Rivos grew, we needed to improve our IP and data management infrastructure for our RISC-V processor development. Our engineers were able to quickly organize our custom IP and ramp up GDP-XL due to its advantages in performance and ease of use compared to other options we considered.”

Biotronik | David Genzer

“Biotronik uses GDP XL design and IP management for maintaining revisions and tracking of internal IP reuse in multiple types of medical implantable products. Internally, GDP-XL manages multi-site reliable tracking of massive IC databases, ultra low power IP Libraries, design test benches, and project tracking info for many highly successful tapeout of IC’s.”

What is Design & IP Management?

Design and IP management platforms provide an efficient mechanism to capture, organize, manage, and share design data and IP — enhancing fast collaboration across design teams while safeguarding sensitive information across multiple generations of designs.